Vivadoに触れてみる

Block Designを利用して設計する

公開日:2023年1月5日

前の記事ではVerilogHDLを用いてLEDを1個を点滅させる機能を作成しました。Vivadoでは、設計したモジュールを視覚的にブロック単位で配置し、Block Diagramとして設計することもできます。Block Designと呼ばれる機能です。本記事では、Block Designを利用して、Blinkモジュールを2個配置し、LEDを2個点滅するように設計を変更します。前の記事のProjectを変更していきます。

Block DesignにBlink モジュールを追加する

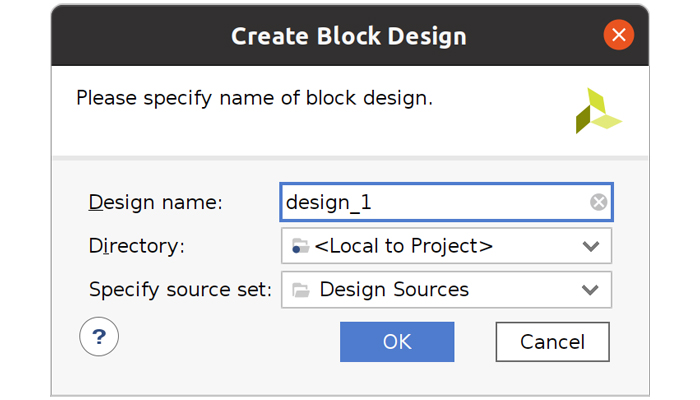

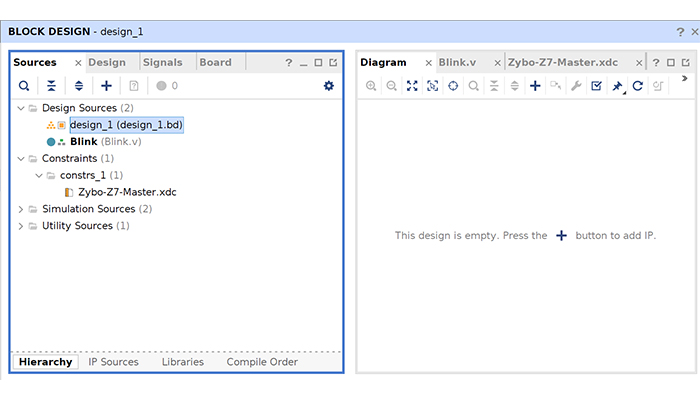

Flow NavigatorのIP INTEGRATORから、Create Block Designを実行します。Design nameは、初期値のままOKとします。

Design Sourcesにdesign_1(design_1.bd)が追加されます。

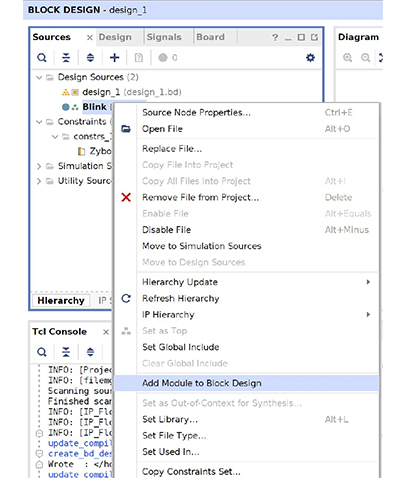

BlinkモジュールをBlock Designに追加します。

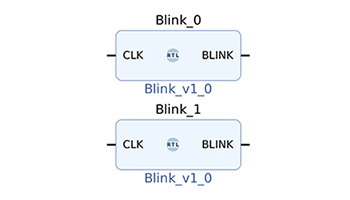

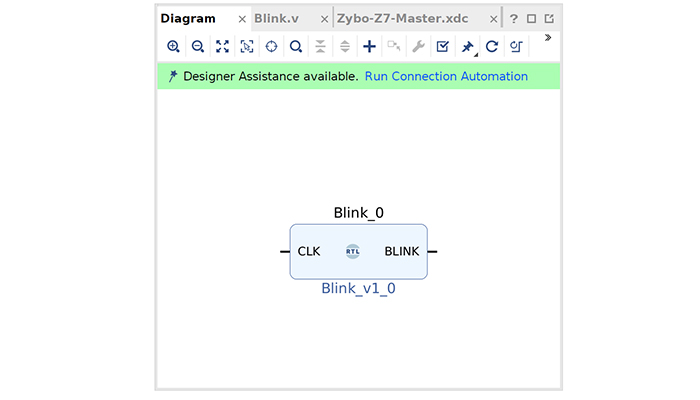

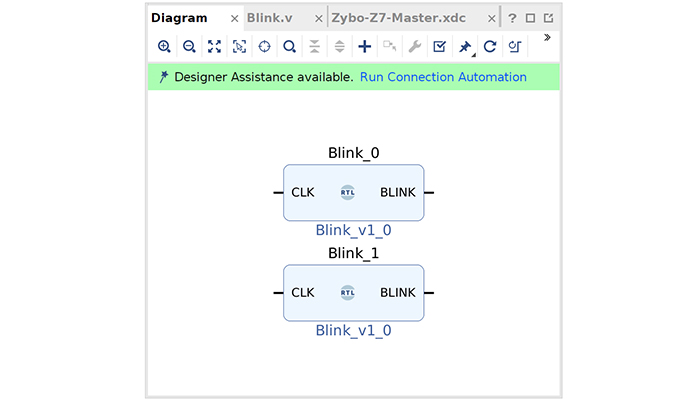

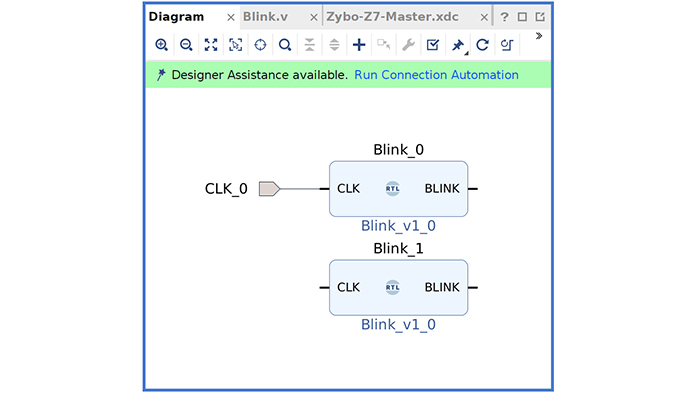

Design SourcesのBlinkを右クリックして、Add Module to Block Designを実行します。DiagramにBlink_0が追加されます。同じ操作を繰り返し、Blinkモジュールをもう一つ追加します。最初に追加したモジュールと区別するため、Blink_1という名前で追加されます。

信号接続する

追加されたモジュールについて信号を接続します。

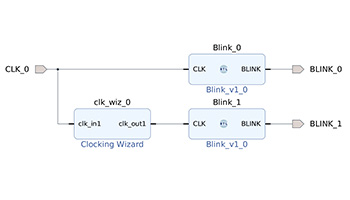

CLKは、Block Designに外部から入力されます。また、BLINK信号は、Block Designの外部に出力されます。この状態をDiagramで表現します。

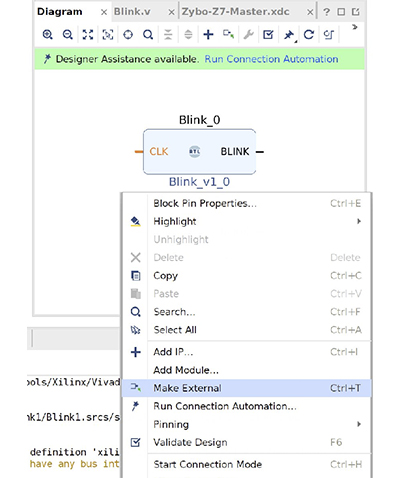

DiagramのBlink_0のCLK端子をクリックしハイライトし、右クリックからMake Externalを実行します。CLK_0というPortが入力として追加されます。Blink1には、同じCLOCKを入力することにしますので、Blink_1のCLK端子からCLK_0に接続してください。

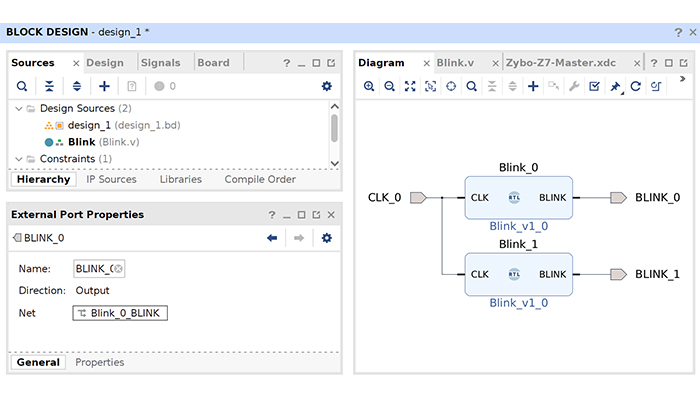

また、BLINKについても、それぞれ個別にMake Externalを実行して出力Portとします。追加したPortのPropertyは、External Port Propertyから確認できます。Port Nameは、自動で割り当てられますが、Propertyから変更することも可能です。

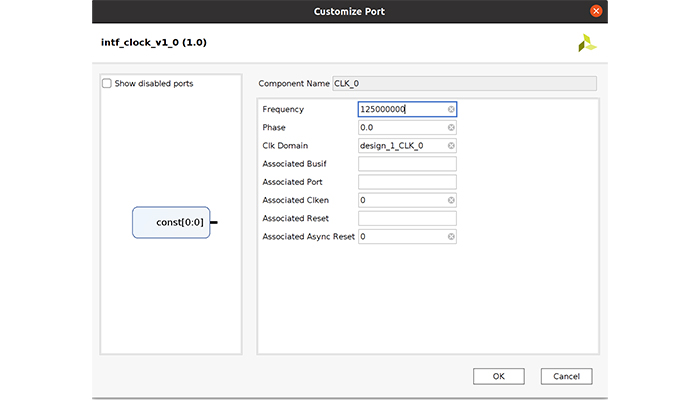

今回のテーマでは特に影響はありませんが、CLK_0の周波数に正しい周波数を記述します。

Zyboの設計上、今回のClockは、125MHzになりますので、Block DesignのCLK_0 portをダブルクリックして、Customized portから、周波数を設定します。

これでBlock Designは完了です。

Create HDL Wrapper

Block Designを作成しただけでは、設計は完了していません。

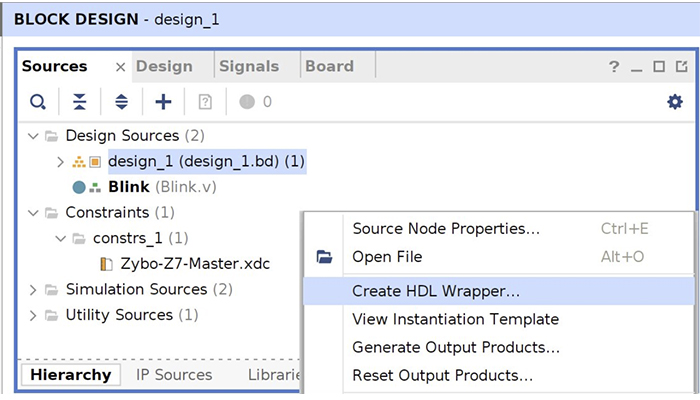

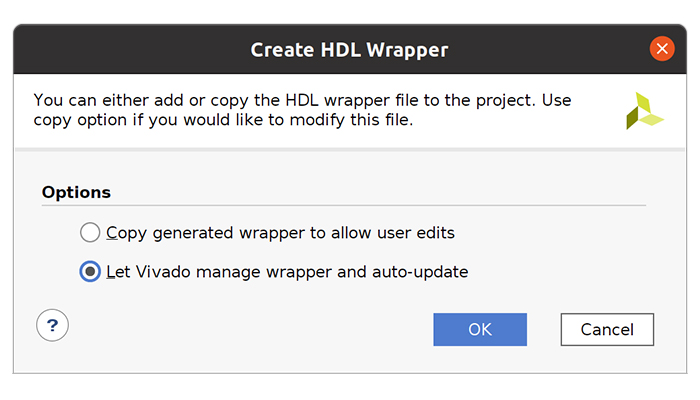

Create HDL Wrapperを実行する必要があります。この操作で、Block Designの上位にTop moduleの役割をするHDLファイルが挿入されます。Design Sourcesのdesign_1(design_1.bd)を右クリックしてCreate HDL Wrapperを実行します。ダイアログが表示されますが、初期値でOKします。

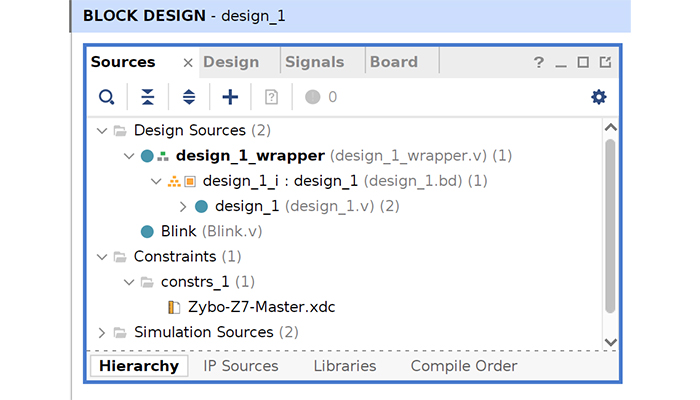

Design Sourcesにdesign_1_wrapper(design_1_wrapper.v)が作成されます。

制約ファイルを変更する

先程作成したdesign_1_wrapper.vを確認します。Top moduleとして、design_1_wrapperが記述されており、入出力に、BLINK_0, BLINK_1, CLK_0 が定義されています。これらの信号を所望の端子に接続する必要があります。

module design_1_wrapper

(BLINK_0,

BLINK_1,

CLK_0);

output BLINK_0;

output BLINK_1;

input CLK_0;

wire BLINK_0;

wire BLINK_1;

wire CLK_0;

design_1 design_1_i

(.BLINK_0(BLINK_0),

.BLINK_1(BLINK_1),

.CLK_0(CLK_0));

endmodule

今回は以下のように接続します。

##Clock signal

set_property -dict { PACKAGE_PIN K17 IOSTANDARD LVCMOS33 } [get_ports { CLK_0 }]; #IO_L12P_T1_MRCC_35 Sch=sysclk

create_clock -add -name sys_clk_pin -period 8.00 -waveform {0 4} [get_ports { CLK_0 }];

##LEDs

set_property -dict { PACKAGE_PIN M14 IOSTANDARD LVCMOS33 } [get_ports { BLINK_0 }]; #IO_L23P_T3_35 Sch=led[0]

set_property -dict { PACKAGE_PIN M15 IOSTANDARD LVCMOS33 } [get_ports { BLINK_1 }]; #IO_L23N_T3_35 Sch=led[1]

動作確認

前の手順と同様に、Generate bitstreamを実行し、動作確認します。LD0, LD1 が同じタイミングで点滅します。

※文中に記載されている各種名称、会社名、商品名などは各社の商標もしくは登録商標です。